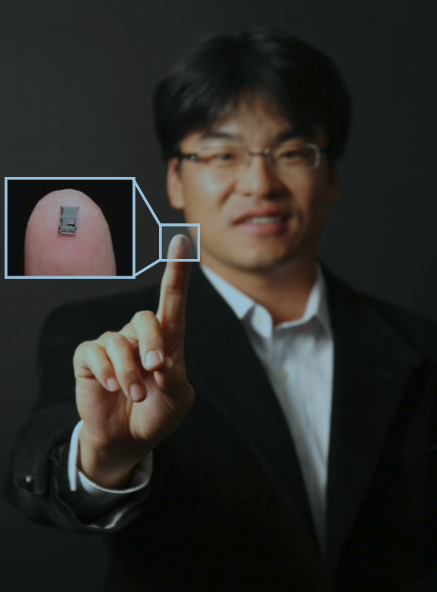

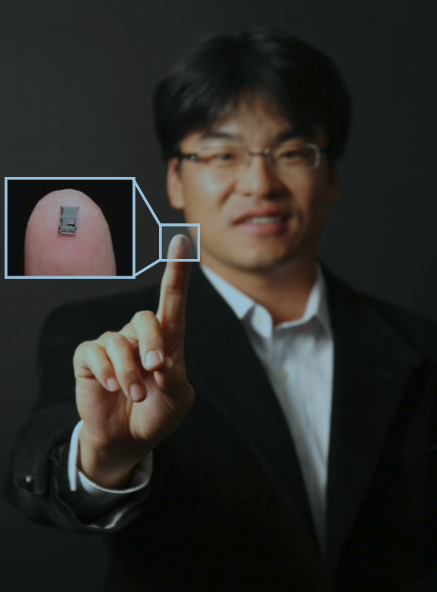

Principal Advisor

Dr. Kyuwon (Ken) Choi

Education

- Ph.D. in Electrical and Computer Engineering, Georgia Institute of Technology (조지아 공대), Atlanta, USA, 2003

- Postdoctoral Fellow in Electrical and Computer Engineering, The University of Tokyo (동경대학교), Tokyo, Japan, 2005

Kyuwon (Ken) Choi is currently a full professor in the Department of Electrical and Computer Engineering at the Illinois Institute of Technology (IIT). He received his Ph.D. in Electrical and Computer Engineering from the Georgia Institute of Technology in 2003. During his doctoral studies, he proposed and conducted several research projects supported by NASA, DARPA, NSF, and SRC, focusing on power-aware computing and communication (PACC).

From 2004, he was a postdoctoral research associate in the Takayasu Sakurai Laboratory at the University of Tokyo, Japan, where he worked on circuit techniques for leakage power reduction. Prior to joining IIT, Dr. Choi served as a senior CAD engineer and technical consultant for low-power system-on-chip (SoC) design at Samsung Semiconductor, Broadcom, and Sequence Design. He has over eight years of industry experience in VLSI chip design, spanning compiler-level to circuit-level development.

In recent years, several processor and control chips utilizing his low-power techniques have been successfully fabricated in deep-submicrometer technologies. Dr. Choi has authored and co-authored more than 80 peer-reviewed journal and conference publications. He is the Director of the VLSI Design and Automation Laboratory (DA-Lab) at IIT, a Senior Member of IEEE, Editor-in-Chief of the Journal of Pervasive Technologies, and a guest editor for Springer and Wiley journals. He has also served as a Technical Program Committee (TPC) member for multiple IEEE circuit design conferences, President of the KSEA Chicago and Midwest Chapter, and Technical Group Director for KSEA Headquarters.